- 软件大小:31KB

- 软件语言:中文

- 软件类型:国产软件

- 软件类别:免费软件 / 编程工具

- 更新时间:2017-07-04 17:48

- 运行环境:WinAll, WinXP, Win7, Win8

- 软件等级:

- 软件厂商:

- 官方网站:http://www.downcc.com/

2603.51M/中文/1.0

255.85M/中文/0.0

7.37M/中文/0.0

1.54M/中文/10.0

7884.79M/中文/2.0

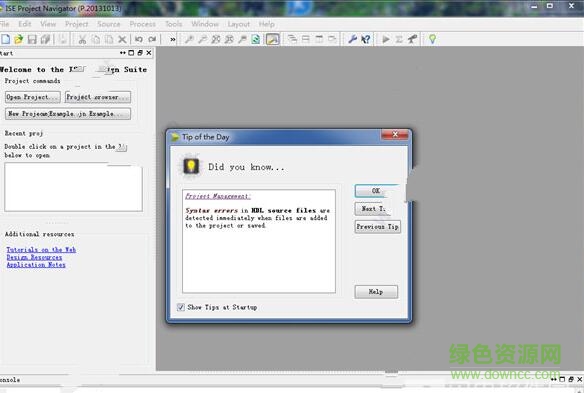

xilinx ise10.1是一款免费的硬件设计工具,可以用来设计仿真挺悠闲,对电路进行模拟测试。集成了多种硬件语言,功能非常给力。需要的用户欢迎在绿色资源网下载安装。

ISE的全称为Integrated Software Environment,即“集成软件环境”,是Xilinx公司的硬件设计工具。相对容易使用的、首屈一指的PLD设计环境 !ISE将先进的技术与灵活性、易使用性的图形界面结合在一起,不管您的经验如何,都让您在最短的时间,以最少的努力,达到最佳的硬件设计。xilinx ise 10.1版本不支持win8等系统,不过在xp系统上完美运行!

1.专门为解决设计人员所面临的时序收敛和生产力这两大艰巨挑战而开发,支持在多台Linux主机上进行分布式处理,可在一天时间里完成更多次实施过程。

2.包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。

3.在硬件设计上应用非常广泛,覆盖从系统级设计探索、软件开发和基于HDL硬件设计,直到验证、调试和pcb设计集成的全部设计流程。

4.通过利用分布式处理和多种实施策略,性能可以提升多达38%。SmartXplorer技术同时还提供了一些工具,允许用户利用独立的时序报告监控每个运行实例。

1.综合(Synthesis)

综合是将行为和功能层次表达的电子系统转化为低层次模块的组合。一般来说,综合是针对VHDL来说的,即将VHDL描述的模型、算法、行为和功能描述转换为FPGA/CPLD基本结构相对应的网表文件,即构成对应的映射关系。

2.验证(Verification)

验证(Verification)包含综合后仿真和功能仿真(Simulation)等。功能仿真就是对设计电路的逻辑功能进行模拟测试,看其是否满足设计要求,通常是通过波形图直观地显示输入信号与输出信号之间的关系。 综合后仿真在针对目标器件进行适配之后进行,综合后仿真接近真实器件的特性进行,能精确给出输入与输出之间的信号延时数据。

3.图形或文本输入(Design Entry)

图形或文本输入包括原理图、状态机、波形图、硬件描述语言(HDL),是工程设计的第一步,ISE集成的设计工具主要包括HDL编辑器(HDL Editor)、状态机编辑器(StateCAD)、原理图编辑器(ECS)、IP核生成器(CoreGenerator)和测试激励生成器(HDL Bencher)等。

请描述您所遇到的错误,我们将尽快予以修正,谢谢!

*必填项,请输入内容